# 科学研究費補助金研究成果報告書

平成21年 5月 8日現在

研究種目:若手研究(B)研究期間:2007~2008 課題番号:19700042

研究課題名(和文)可変パイプライン構造を持つ高性能・低消費電カプロセッサに関する研究

研究課題名 (英文) A Study on Low Energy and High Performance Processor using

Variable Stages Pipeline Architecture

研究代表者 佐々木 敬泰 (SASAKI TAKAHIRO)

三重大学・大学院工学研究科・助教

研究者番号: 20362361

#### 研究成果の概要:

近年、ノート・パソコンや携帯電話等の携帯端末においても高性能プロセッサが搭載されつつ ある。例えば携帯電話の内蔵カメラで撮影した動画を送信するには複雑かつ膨大な処理が必要 となる。一方でこれらの携帯端末はバッテリにより駆動することが多いため、高性能化に伴う 消費電力の増大が問題となっている。そこで、本研究ではプロセッサ内部構成の動的な変更と 無駄なスイッチングを削減することで、従来手法と比較してプロセッサの高性能化と低消費電 力化の両立を達成した。

# 交付額

(金額単位:円)

|         | 直接経費        | 間接経費     | 合 計         |

|---------|-------------|----------|-------------|

| 2007 年度 | 400, 000    | 0        | 400, 000    |

| 2008年度  | 1, 400, 000 | 420, 000 | 1, 820, 000 |

| 年度      |             |          |             |

| 年度      |             |          |             |

| 年度      |             |          |             |

| 総計      | 1, 800, 000 | 420, 000 | 2, 220, 000 |

研究分野:計算機アーキテクチャ

科研費の分科・細目:情報学・計算機システム・ネットワーク

キーワード:低消費電力、プロセッサ設計、システムオンチップ、計算機システム

# 1. 研究開始当初の背景

近年、ノート・パソコンや PDA、携帯電話等の携帯端末においても高性能プロセッサが搭載されつつある。例えば携帯端末を用いて、複雑かつ膨大な処理を伴う動画像のエンコード/デコード、およびその送受信を行うことが現実化している。そして、ユビキタス・コンピューティング環境の広がりにより、この傾向はますます強くなりつつある。これらの要求を満たすべく、プロセッサの高性能化やマルチプロセッサ化に関する研究が広

く行われてきた。一方でこれらの携帯端末は バッテリにより駆動することが多いため、高 性能化に伴う消費電力の増大が問題となっ ている。

現在の代表的な低消費電力化手法の一つとして DVS があげられる。 DVS は動的に電源電圧と動作周波数を制御することによって消費電力を削減する。消費電力は電源電圧の2乗に比例するため、電源電圧を低下させることは消費電力を大きく削減することに繋

がる。しかし、LSIの電源電圧は年々低下しており、将来的に閾値電圧の制御などの問題から電源電圧を低下させることのできる変化幅は小さくなる。そのため DVS による消費電力の削減効率は低下することになる。そこで、DVS に代わって、電源電圧に依存しないアーキテクチャレベルの低消費電力化手法として、PSU (Pipeline Stage Unification)や DPS (Dynamic Pipeline Scaling)のように動的にパイプラインステージを変化させる手法がある。しかし、この手法もステージ統合時にグリッチが発生し、消費エネルギーが増加するという問題がある。

# 2. 研究の目的

本研究では上記問題を解決する高性能・低消費電力プロセッサの開発を目指している。一般に集積回路の消費電力はトランジスタのスイッチングに伴う動的な電力消費と、起フシジスタの漏れ電流(リーク電流)に起のする静的な電力消費に分けられる。近年の機細化プロセスではリーク電流による電力対してよるでは関盟となっているが、この問題に対しては様々な研究が行われており、従来は引費電力の削減ができるようになってはないできるよば MOSFET のゲート構造を三次で化する FinFET や、ゲート酸化膜に誘電を用いることが明らかにされている。

しかし、トランジスタのスイッチングに伴う動的な電力消費については、電力消費の大部分を占めるにもかかわらず、本質的に削減し難いものとしてあまり研究が行われていなかった。そこでこの問題を解決するために、研究代表者らは動的な電力消費のうち、グリッチ(ゲート遅延や配線遅延により発生する信号線の変化)に起因する冗長なスイッチングを削減することで消費電力の低減を目指す。

#### 3. 研究の方法

本研究では、スーパスカラ・プロセッサ、スーパパイプライン・プロセッサを含むパイプライン・ベースのプロセッサを想定し、負荷が低い場合に動的にクロック周波数を低下させ、かつパイプライン・レジスタのいくつかをバイパスした上で不要になったパイプライン・レジスタを停止することによりまうにかりできるように改良した上で、2)パイプライン統合時に発生するグリッチの増加を緩和するために LDS-cell という独自の回路を導入することで、プロセッサの高性能化と低消

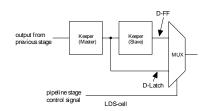

費電力化の両立を目指す。図2にLDS-cellの概要図を示す。LDS-cellはDFFとラッチの機能を併せ持つセルであり、通常モードではパイプライン・レジスタとして、低電力モード時にはグリッチの電波を抑制するためにラッチとして動作させることで高性能と低消費電力の両立を実現している。

本研究では、以下のような手順を追って研究を進めていく。

# (1)シミュレーション評価:

シミュレーション評価による評価環境の 詳細化を行う。本研究の最終的な目的は、LSI を試作した上で提案手法の有効性を明らか にすることであるが、LSI 試作には膨大な予 算と多大な設計時間が必要となる。そこで、 まずシミュレーション評価を行い、高性能と 低消費電力を実現するためのシステム構成 を検討する。

#### (2)モード切替手法の確立:

図1:可変パイプライン段数の概要

図2:LDS-cell の概要

次にモード切り替え手法を確立する。本提案手法は、性能は低いが低消費電力で演算できる Low Energy (LE)モードと消費電力は高いが高速に演算できる High Speed (HS)モードをプログラムの実行状況によって適応的に切り替えることによって低消費電力と高性能の両立を目指している。そこで、プロセッサの状態を観測し、最適なモードを選択する手法を開発する。

# (3)詳細設計、および評価:

(2)と並行して提案手法を含むプロセッサの詳細設計を進める。(1)、(2)の結果を分析した上で、詳細な仕様を決め、LSIの試作評価を行う。これにより、提案手法が現実的な制約条件下で実現できることを示す。具体的にはベースとなる MIPS R3000 互換プロセッサを改造し、HS モード時には多段のパイプラインプロセッサとして、LE モード時は少段の

パイプラインプロセッサとして動作するようにする。その後、提案手法である可変パイプライン段数プロセッサをLSI上にレイアウト設計した上で、電子回路シミュレータSynopsys NanoSimを用いて消費電力を計算し、パイプライン段数の動的変更による低消費電力化の効果を解析する。最後に、ROHM社の0.18um CMOSプロセスを用いてLSI試作を行い提案手法が現実的な制約条件下で実現できることを明らかにする。なお、LSIの試作は東京大学大規模集積システム設計教育研究センターを通しローム(株)および凸版印刷(株)の協力のもとで行う。

#### 4. 研究成果

以下に本研究で得られた成果をまとめる。

# (1)シミュレーション評価:

一般にプロセッサの性能や消費電力はパ イプライン段数や演算資源数、命令フェッチ 幅、キャッシュ性能などに依存する。そこで、 まず低消費電力を高性能を両立させるのに 適したプロセッサ構成を検討するために 様々なシミュレーション評価を行った。この 課程において、高性能と低消費電力を両立す るキャッシュシステムを提案し、その有効性 を示した。具体的には、プログラムの実行過 程に応じて必要とされる性能は動的に変動 する。可変パイプライン段数アーキテクチャ では、要求性能が低い場合にパイプラインス テージを統合し、クロック周波数を低下させ ることで消費電力低減を実現しているが、キ ヤッシュメモリの構成は変わらないため、キ ャッシュシステムに関しては性能が冗長に なる。

そこで、動的にキャッシュの要求性能を判断し、あまり性能が必要ないと判断したときにキャッシュの半分をスリープモードに移行し1つ下位のレベルの排他的キャッシュとして動作させる事で、消費電力の削減と性能の維持を両立させる手法を提案した。本研究で行ったシミュレーション結果によると、可変レベルキャッシュは従来の低電力キャッシュの一つであるDRIキャッシュと比較してエネルギー遅延積(ED積)で12%程度性能向上することが分かった。本研究の成果は学会発表④と学会発表⑥で公表済みである。

#### (2)モード切替手法の確立:

可変パイプライン段数アーキテクチャは、プロセッサの負荷に応じてパイプライン段数を動的に変更する手法であるため、実行時のプロセッサの状態を把握し、適切なモードを決定することが不可欠である。そこで、提案手法を実用化する上で不可欠となるパイプライン段数切換えスケジューラを作成し、評価を行った。実装したスケジューラは、プ

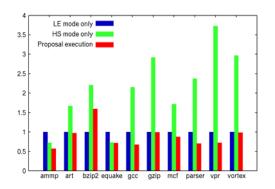

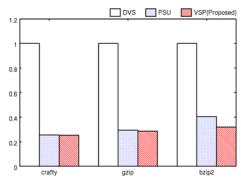

ロセッサの負荷に応じて、低消費エネルギーかつ高性能を両立するようにパイプライン 段数を変更するよう制御を行うものである。 このスケジューラを VSP に組み込み評価を行った。図3に評価結果を示す。

図3:動的モード切替スケジューラ導 入による効果

図3は横軸がベンチマークプログラム、縦軸がエネルギー遅延積で、LEモードに固定した場合を1として正規化した。図3より、固定的な少段パイプライン構成を採用した低消費電力向けプロセッサ(LE mode only)と比較して、スケジューラを組み込んだ方式(Proposal execution)は電力遅延積において約20%の改善が得られた。本研究の成果は学会発表③で公表済みである。

# (3) 詳細設計、および評価:

これまでに行ってきた予備評価の結果を 分析した上で、可変パイプライン段数アーキ テクチャの有効性を示すための試作 LSI の詳 細設計を行った。まず、可変パイプライン段 数アーキテクチャを用いたプロトタイププ ロセッサである VSP プロセッサの詳細設計に ついて述べる。 VSP プロセッサは MIPS R3000 と命令互換性を持つ。 VSP プロセッサはパイ プラインステージを統合することによって 動的にパイプラインステージを変化させる ことができる。 さらに LDS-cell を搭載する

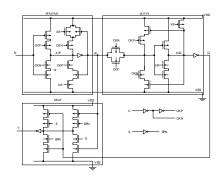

図4:LDS-cell の回路図

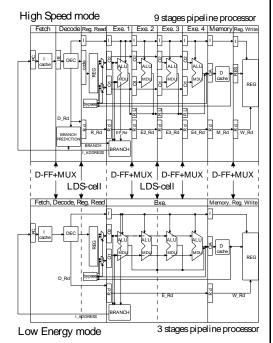

図 5:可変パイプライン段数アーキテク チャのブロック図

ことによってパイプラインステージ統合時のグリッチの増加を緩和できる。図4に設計した LDS-cell の回路図を、図5に LDS-cell を組み込んだ VSP プロセッサのブロック図を示す。

前述の通り、VSP プロセッサはパイプライン段数の違いによって High Speed (HS) モードと Low Energy (LE) モードの2つのモードを持つ。これら2つのモードの仕様は以下の通りである。

# HS モード

- ・ 9段パイプラインであり、LDS-cell はパイプライン・レジスタとして動作する。

- デコードステージに gshare 分岐予測ユニットを搭載しており、分岐ミスペナルティは3サイクルである。

- ・ 無条件分岐は分岐予測ユニットにおいて 100%の分岐予測が可能である。

- ・ インターロックと演算結果のフォワーディング機構を搭載している。

# LE モード

- ・ 3段パイプラインであり、LDS-cell はグ リッチの緩和を行うD-ラッチとして動作 する。

- HS モードの 1/4 の周波数で動作する。

- ・ 遅延分岐、遅延ロード、フォワーディングによって分岐ペナルティやデータ依存によるインターロックが発生しない。

- ・ 分岐予測ユニットは使用しないので停止する。

- 分岐予測ユニットやバイパスされて使用

図 6:可変パイプライン段数プロセッサ のレイアウト結果

図7: 試作した LSI のチップ写真

図8:提案手法の効果(LE モード)

しなくなったパイプライン・レジスタの クロックを止めることでパイプライン・ レジスタで消費されるエネルギーを削減 することができる。

このような構成をもつプロセッサを詳細 設計し、LSI 試作を行った。図6に試作した LSI のレイアウト図を、図7にチップ写真を 示す。

試作した LSI のレイアウト情報から回路情報を抽出し、詳細な回路シミュレーションにより性能評価を行った。図8に評価結果を示す。図8は横軸がベンチマークプログラム、縦軸が DVS を1として正規化した電力遅延積である。

評価結果より、現在広く用いられている DVS プロセッサと比較して 70%の電力遅延積 の削減を達成できることがわかる。また、提 案手法を適用することによる回路の増加は、 DVS と比較して僅か 3%程度であることが明ら かになった。本研究の成果は雑誌論文①、お よび学会発表①と学会発表②、学会発表⑤で 公表済みである。

### (4)今後の展望

今回試作した LSI は時間の都合上、(2)の成果を十分に反映できていない。また、学会発表①で公表した成果を導入していない。そこで、今後は本研究で得られた成果をもとに、更なる低消費電力プロセッサの開発に繋げていく予定である。

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# 〔雑誌論文〕(計1件)

① Takahiro Sasaki, Yuji Ichikawa, Tetsuo Hironaka, Toshiaki Kitamura and Toshio Kondo, Evaluation of Low Energy and High Performance Processor using Variable Stages Pipeline Technique, IET Journal of Computer and Digital Techniques, Vol.2, No.3, pp.230-238, 2008 (查読有 り)

# 〔学会発表〕(計6件)

中林 智之、佐々木 敬泰、大野 和彦、 近藤 利夫、可変段数パイプラインアー キテクチャ (VSP)の更なる低消費電力化 手法の提案と LSI 設計、CPSY2008-34、 pp. 29-34、2008 年 10 月 31 日、広島県広 島市。

- ② 秋田 直己、<u>佐々木 敬泰</u>、大野 和彦、 近藤 利夫、高性能と低消費電力を両立 する可変パイプライン構造の再構成デ バイスへの適用、情報処理学会アーキテ クチャ研究会、2008 年 8 月 6 日、佐賀県 佐賀市。

- ③ 野村 和正、<u>佐々木 敬泰</u>、大野 和彦、 近藤 利夫、可変パイプライン段数プロ セッサの段数切替えスケジューラの設 計と評価、情報処理学会アーキテクチャ 研究会、2008年8月6日、佐賀県佐賀市。

- ④ 恩賀 琢也、<u>佐々木 敬泰</u>、大野 和彦、 近藤 利夫、可変レベルキャッシュの書 き戻しペナルティ軽減手法の提案、情報 処理学会研究報告、 情報処理学会アー キテクチャ研究会、2007 年 11 月 22 日、 福岡県北九州市。

- ⑤ 秋田 直己、佐々木 敬泰、大野 和彦、近藤 利夫、VSP(Variable Stages Pipeline)の低消費電力、高性能化、情報処理学会研究報告、情報処理学会アーキテクチャ研究会、2007年8月2日、北海道旭川市。

- ⑥ 恩賀 琢也、佐々木 敬泰、大野 和彦、 近藤 利夫、キャッシュ階層動的切り替 えによる低消費電力化、 情報処理学会 アーキテクチャ研究会、2007 年 8 月 2 日、北海道旭川市。

- 6. 研究組織

- (1)研究代表者

佐々木 敬泰 (SASAKI TAKAHIRO) 三重大学・大学院工学研究科・助教 研究者番号:20362361

- (2)研究分担者

- (3)連携研究者